printf("ho_tari\n");

1일차 본문

2025.06.30

Vivado와 Vitis에 대해서

Vivado와 Vitis는 모두 Xilinx가 FPGA(Fiel-Programmable Gate Array) 개발을 위해 제공하는 도구. 각 도구의 주요 사용 용도와 차이는 다음과 같다.

Vivado: Xilinx의 FPGA 디자인 및 논리 합성 도구. 이 도구를 사용하면 디자인을 직접 FPGA에 구현하고, 논리를 합성하며, 타이밍 분석을 수행하고, FPGA의 물리적 배치를 정의할 수 있다. 또한, RTL(RTL, Register Transfer Level) 설계를 위한 하드웨어 설명 언어, 예를 들어 VHDL이나 Verilog를 사용하여 사용자가 직접 하드웨어 로직을 설계 할 수 있다.

Vitis : Xilinx의 소프트웨어 설계 스택으로, FPGA에서 실행되는 애플리케이션을 개발하는 데 사용. Vitis는 다양한 종류의 처리 요소(예: CPUs, GPUs, FPGAs)에 대해 단일 개발 환경을 제공. 소프트웨어 개발자가 C, C++, OpenCL, Python 등의 고수준 언어를 사용하여 FPGA에 애플리케이션을 개발하고 최적화할 수 있다. Vitis는 또한 라이브러리 세트를 제공하여 알고리즘을 빠르게 구현하고, 기계 학습, 이미지 처리, 데이터 분석 등의 고수준 도메인에 대한 최적화를 제공.

요약하면, Vivado는 FPGA의 하드웨어 설계 및 구현을 위한 도구이고, Vitis는 FPGA에서 실행되는 소프트웨어 애플리케이션을 개발하는 도구이다. 따라서 이 두 도구는 FPGA 개발의 다른 측면을 각각 다루며, 종종 함께 사용되어 하드웨어와 소프트웨어를 모두 개발하는 통합 개발 환경을 제공합니다.

Xilinx Zynq FPGA에서는 Programmable Logic (PL)과 Processing System (PS)이라는 두 가지 주요 구성 요소가 있다.

영역이다. 이 PL 영역은 VHDL, Verilog 등의 하드웨어 설명 언어를 사용하여 구현되며, 이는 Vivado와 같은 도구를 통해 수행된다.

(2) Processing System (PS): Zynq FPGA에 내장된 고정된 하드웨어 구성 요소로서, 일반적으로 ARM 기반의 프로세서 시스템이다. PS는 운영 체제를 실행하고, 소프트웨어 애플리케이션을 실행하며, PL과 상호 작용하는 데 사용된다. 이 부분은 주로 고수준 언어(C, C++, Python 등)를 사용하여 개발하며, 이는 Vitis와 같은 도구를 통해 수행된다.

- Vivado는 주로 PL을 설계하고 구현하는 데 사용되며,

- Vitis는 PS에서 실행되는 소프트웨어를 개발하는 데 사용.

그러나 두 시스템은 서로 밀접하게 연결되어 있으며, 종종 Vivado를 사용하여 PS와 PL 사이의 인터페이스를 설정하고, Vitis를 사용하여 PS에서 실행되는 소프트웨어와 PL에서 실행되는 하드웨어 로직 간의 상호 작용을 관리한다.

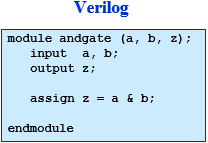

HDL : Hardware Description Language

디지털 논리 회로의 문자 표현

- schematic보다 만들거나 고치기 쉬움

- HDL 설계시에는 항상 schematic을 생각해야 함

HDL은 programming languages가 아님

- 매우 비슷하게 보이지만 프로그램처럼 작성하면 안됨

- Verilog 문법은 C와 상당히 유사함

- 뛰어넘어야 할 가장 중요하고 어려운 개념

- C : 순차적 실행

- HDL : 병렬적 실행

- 컴파일 방법은 비슷함

- C : Source → 컴파일 → 실행파일

- HDL : Source → 컴파일 → 시뮬레이션 → 합성(synthesis) → Hardware

Verilog의 특징

- C언어와 유사하다

- 코딩량이 10~30% 적다

- 회사에서는 Verilog가 우세하다

- 많은 IP들이 Verilog로 되어 있다

- VHDL은 표현이 너무 엄격

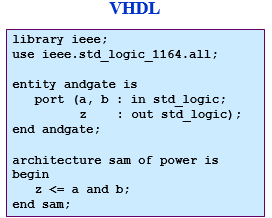

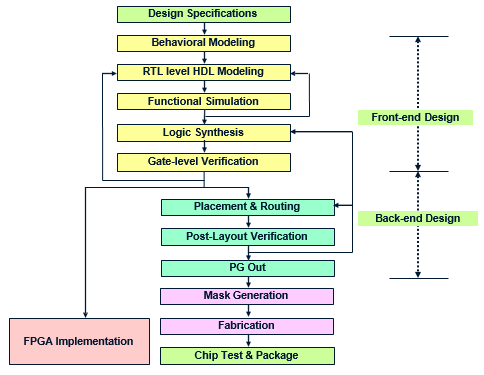

System IC 설계과정

설계사양 결정

- 회로의 기능, 동작성능, 동작 주파수, 칩 면적 및 전력 소모 목표치, 시험 범주(test coverage), 설계 기간, NRE(Non-Recurring Engineering) 비용, 칩 단가 등이 포함된 설계 목표

- 설계될 시스템의 분할, 적용될 알고리즘과 아키텍처, 데이터 입/출력 및 제어 신호들의 타이밍, 입력/출력 신호의 이름과 비트 폭, 리셋 및 enable 신호, 클록 신호에 대한 정의 등을 포함

행위수준(Behavioral level) 모델링 및 검증

- 상세 설계 이전에 설계사양을 확인할 수 있도록 시스템의 전체기능을 모델링하고 검증하는 과정

- 설계사양에서 정의된 기능의 만족 여부, 입/출력 인터페이스의 호환성, 국제표준규격의 만족 여부 등을 검증

- C언어, Verilog, SystemVerilog, SystemC 등을 사용

HDL 코딩 (RTL 설계)

- RTL (Register Transfer Level) 모델링을 통한 상세 설계

- 논리합성 툴에서 합성 가능한 코드로 개발

- 합성 가능한 RTL 설계

- 모듈을 이용한 구조적 모델링

- 합성이 지원되지 않는 구문이나 파일 입/출력 구문은 사용 금지

- 최적의 하드웨어가 합성되도록 모델링

- 검증을 위한 테스트 벤치 (test bench) 작성

HDL 시뮬레이션 (기능 검증)

- RTL 모델이 설계사양을 만족하는지 확인하기 위한 검증

- 회로 내부의 지연이 고려되지 않은 기능 수준의 검증

- 회로의 기능을 정확하게 검증할 수 있는 테스트 벤치의 작성이 중요

- 테스트벤치 작성은 설계자의 능력과 숙련도가 요구됨

- 최근 시스템 복잡도가 급격히 증가함에 따라 검증 작업이 설계 과정의 병목이 됨

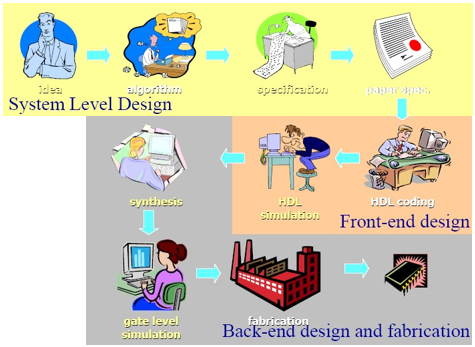

논리합성 (synthesis)

- RTL 수준의 HDL 코드를 게이트 수준의 논리회로로 변환하는 과정

- 합성 조건들이 명시된 제한조건과 target library가 사용됨

- Constraint

- 합성되는 회로의 목표 동작 주파수, 면적, 클록신호 사양, 입/출력 신호 사양, 환경 변수 및 설계 규칙 등 논리합성에 사용될 조건들

- Target library

- 합성에 사용되는 라이브러리

- 특정 회사의 FPGA 디바이스 또는 특정 회사의 셀 라이브러리

논리합성

논리합성 단계

- HDL 코드를 읽어 문법적인 오류를 분석하고 구문을 해석하여 논리 게이트로 변환하는 단계

- 최적화 알고리즘을 적용하여 회로를 간소화시키는 최적화 단계

- 셀 라이브러리로 매핑하는 단계

게이트 수준 검증

- 합성이 완려되면 게이트 수준의 netlist가 얻어지며 합성에 사용된 라이브러리의 특성이 합성된 회로에 반영됨

- RTL 수준 검증에서 사용되었던 테스트 벤치를 동일하게 적용하여 논리 및 타이밍을 검증

- 정적 타이밍 분석 (Static Timing Analysis; STA)

- 합성된 회로의 신호경로를 중심으로 타이밍을 분석

- 시뮬레이션 벡터가 사용되지 않음

- 레지스터의 setup time과 hold time의 위반 여부를 분석함

레이아웃 설계

- 논리합성을 통해 생성된 게이트 수중netlist를 마스크 제작에 사용될 레이아웃 도면으로 변환하는 과정

- 자동 배치/배선 툴

- 칩 제작 공정에 맞게 미리 설계된 표준 셀 라이브러리, RAM, ROM 등의 매크로 셀, I/O 패드 셀과 설계자가 지정한 타이밍 조건을 적용하여 최적화된 레이아웃 도면을 생성

Post-layout 검증

- 레이아웃으로부터 셀과 배선에 의한 지연 특성을 추출하여 타이밍 특성이 고려된 post-layout 검증

- 게이트 수준 타이밍 시뮬레이션, 레이아웃의 기생 효과를 고려한 STA, 각종 설계 규칙검사 등을 통해 설계의 정확성을 검증

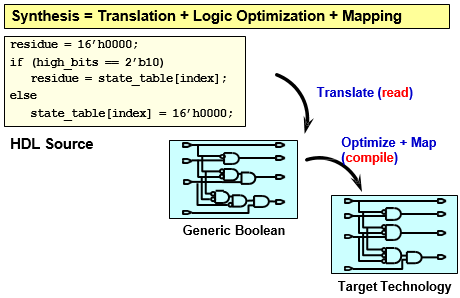

RTL 수준과 Gate 수준 Verilog

HDL 기반 설계의 장점

- 설계 시간의 단축

- 초기 설계과정에서의 설계오류 수정이 용이

- 합성에 의한 회로 생성과 설계 변경이 용이

- 설계의 질 향상

- 우수하고 광범위한 하드웨어 기술 능력, 상위 수준의 설계 가능

- 다양한 설계기법의 검색에 의한 최적화 도달

- 선택적 최적화 기법을 이용한 합성 설계

- 특정 설계기술이나 공정과 무관한 설계

- 특정 ASIC 제조업체 및 구현기술과 무관한 설계 가능

- 동일한 HDL 설계의 다른 라이브러리 이용한 합성

- 신속한 하드웨어 원형화(prototyping) 가능

- 낮은 설계 비용

- 상위레벨 설계도구의 사용에 따른 설계 생산성 향상

- 설계기간의 단축에 따른 설계비용의 감소

- 설계자산의 재사용에 의한 설계비용의 감소

- 표준 HDL 및 사용자의 확대

- IEEE 표준인 동시에 미국 정부의 공인 HDL

- 전세계적으로 설계 및 설계정보 교환의 수단으로 사용이 확대

- 효율적인 설계관리

- HDL 언어의 구조적 설계 기능을 이용한 전체 설계의 기능별 분할 설계 및 설계관리 및 문서화 용이

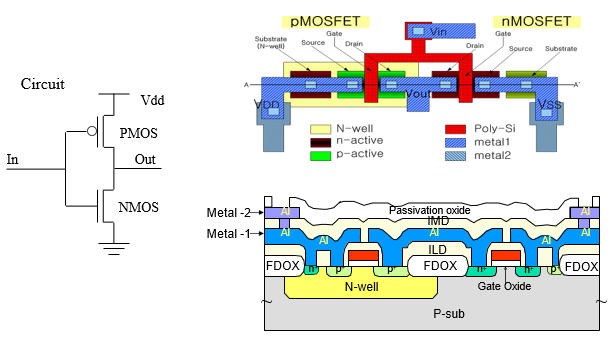

CMOS (Complementary Metal Oxide Semiconductor)

- NMOS (N-Type Metal Oxide Semiconductor) transistors

- PMOS (P-Type Metal Oxide Semiconductor) transistors

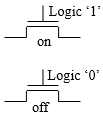

NMOS Transistor

- Logic '1'을 gate에 가하면 'on'

- Logic '0'을 gate에 가하면 'off'

PMOS Transistor

- Logic '1'을 gate에 가하면 'off'

- Logic '0'을 gate에 가하면 'on'

CMOS 인버터

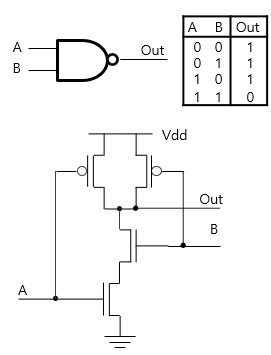

CMOS NAND 게이트

CMOS NOR 게이트

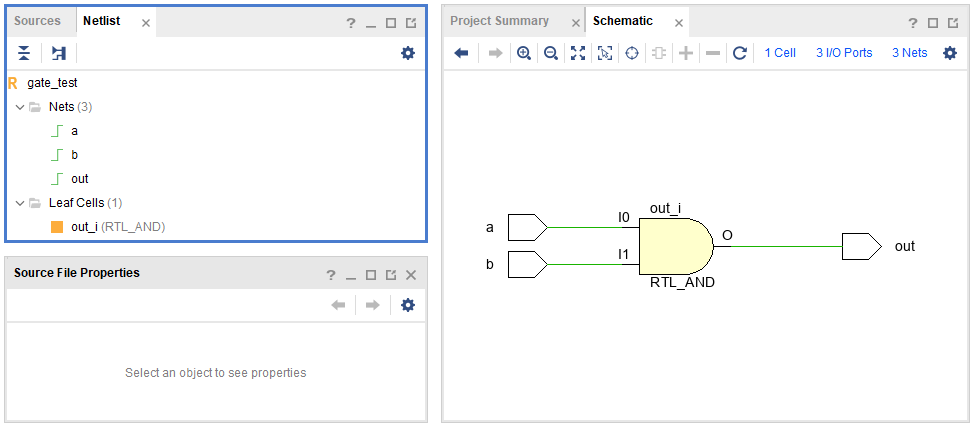

gate_test.v (and)

`timescale 1ns / 1ps // 10.222

module gate_test(

input wire a,

input b, // 생략하면 wire 아무런 언급 안하면 1bit

output out

);

assign out = a & b;

endmodule

gate_test.v (or)

`timescale 1ns / 1ps // 10.222

module gate_test(

input wire a,

input b, // 생략하면 wire 아무런 언급 안하면 1bit

output out

);

assign out = a | b;

endmodule

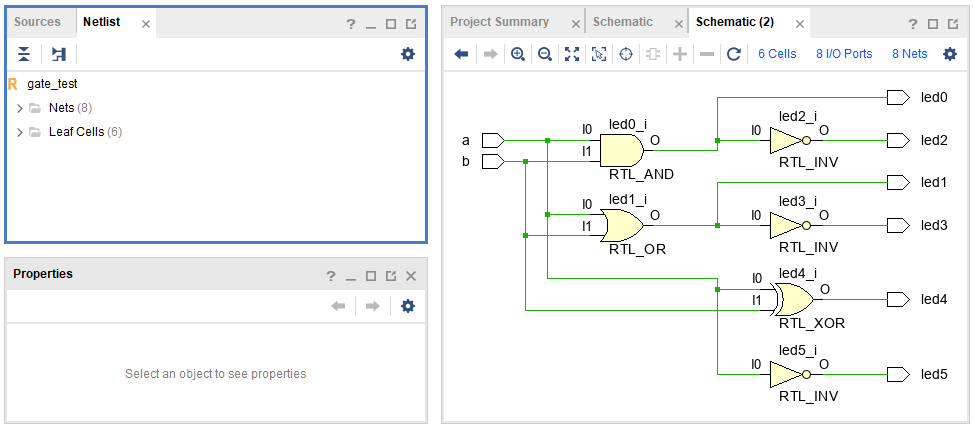

`timescale 1ns / 1ps // 10.222

module gate_test(

input wire a,

input wire b, // 생략하면 wire 아무런 언급 안하면 1bit

output led0,

output led1,

output led2,

output led3,

output led4,

output led5

);

assign led0 = a & b;

assign led1 = a | b;

assign led2 = ~(a & b);

assign led3 = ~(a | b);

assign led4 = a ^ b;

assign led5 = ~a;

endmodule

gate_test.v (배열)

`timescale 1ns / 1ps // 10.222

module gate_test(

input wire a,

input wire b, // 생략하면 wire 아무런 언급 안하면 1bit

output [5:0] led

// output led0,

// output led1,

// output led2,

// output led3,

// output led4,

// output led5

);

assign led[0] = a & b; // and

assign led[1] = a | b; // or

assign led[2] = ~(a & b); // nand

assign led[3] = ~(a | b); // nor

assign led[4] = a ^ b; // xor

assign led[5] = ~a; // not a

endmodule

'(Telechips) AI 시스템 반도체 SW 개발자 교육 > Verilog HDL' 카테고리의 다른 글

| 8일차 (0) | 2025.07.09 |

|---|---|

| 6일차 (0) | 2025.07.07 |

| 4일차 (0) | 2025.07.04 |

| 3일차 (0) | 2025.07.02 |

| 2일차 (0) | 2025.07.02 |