printf("ho_tari\n");

12일차 본문

2025.07.15

UART(Universal Asynchronous Receiver/Transmitter)

비동기 직렬 통신 방식으로, 마이크로컨트롤러(MCU), FPGA, 센서 등에서 널리 사용되는 통신 방법

■ UART 통신의 특징

- 비동기식(Asynchronous): 클럭 신호를 별도로 사용하지 않음

- 직렬 통신: 데이터를 한 비트씩 순차적으로 전송

- Full-Duplex 가능: 송신(TX)과 수신(RX)을 동시에 처리 가능

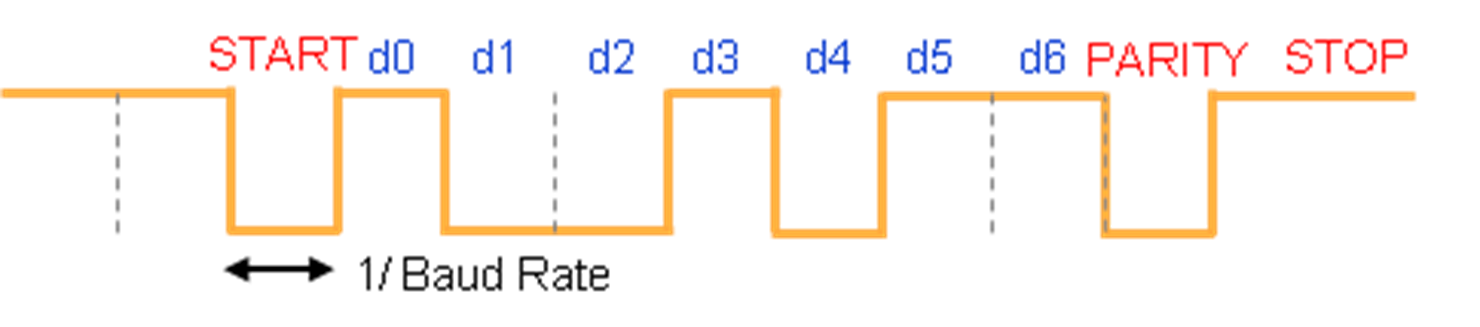

■ UART 데이터 통신 규격

시작 (START) 비트: 통신의 시작을 의미하며 한 비트 시간 길이만큼 0을 유지한다.

데이터 비트: 5~8비트의 데이터 전송을 한다.

패리티 (PARITY) 비트: 오류 검증을 하기 위한 패리티 값을 생성하여 송신하고 수신쪽에서 오류 판단한다.

끝 (STOP) 비트: 통신 종료를 알린다.

보드레이트 (Baud Rate): Baud Rate는 통신에서 1초에 전송하는 심볼의 수이다.

비동기 통신에서는 별도의 데이터의 시작과 끝을 위한 별도의 클럭을 사용하지 않고 1bit의 데이터를 확인 하기 위하여 여러 개의 샘플(16개)를 취하여 비트의 시작과 끝을 판단 한다. 2배속 모드는 비트 데이터 확인을 위해서 샘플의 수를 절반(8개)로 줄여 전송속도를 2배로 증가 시키는 방법이다.

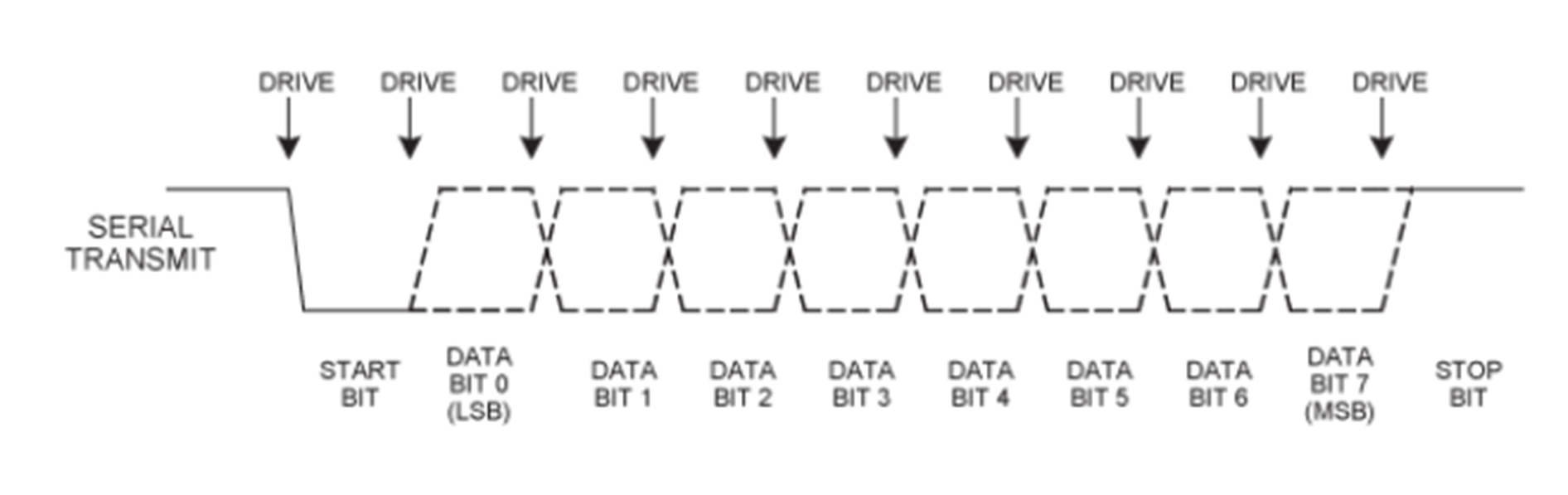

송신 (TX)

보낼 데이터(byte)를 프레임 구조로 구성

각 비트를 일정한 속도로 순차적으로 전송

수신 (RX)

Start Bit의 Falling Edge를 감지 → 샘플링 시작

정해진 시간 간격으로 Data/Parity/Stop Bit 수신

UART의 장점 / 단점

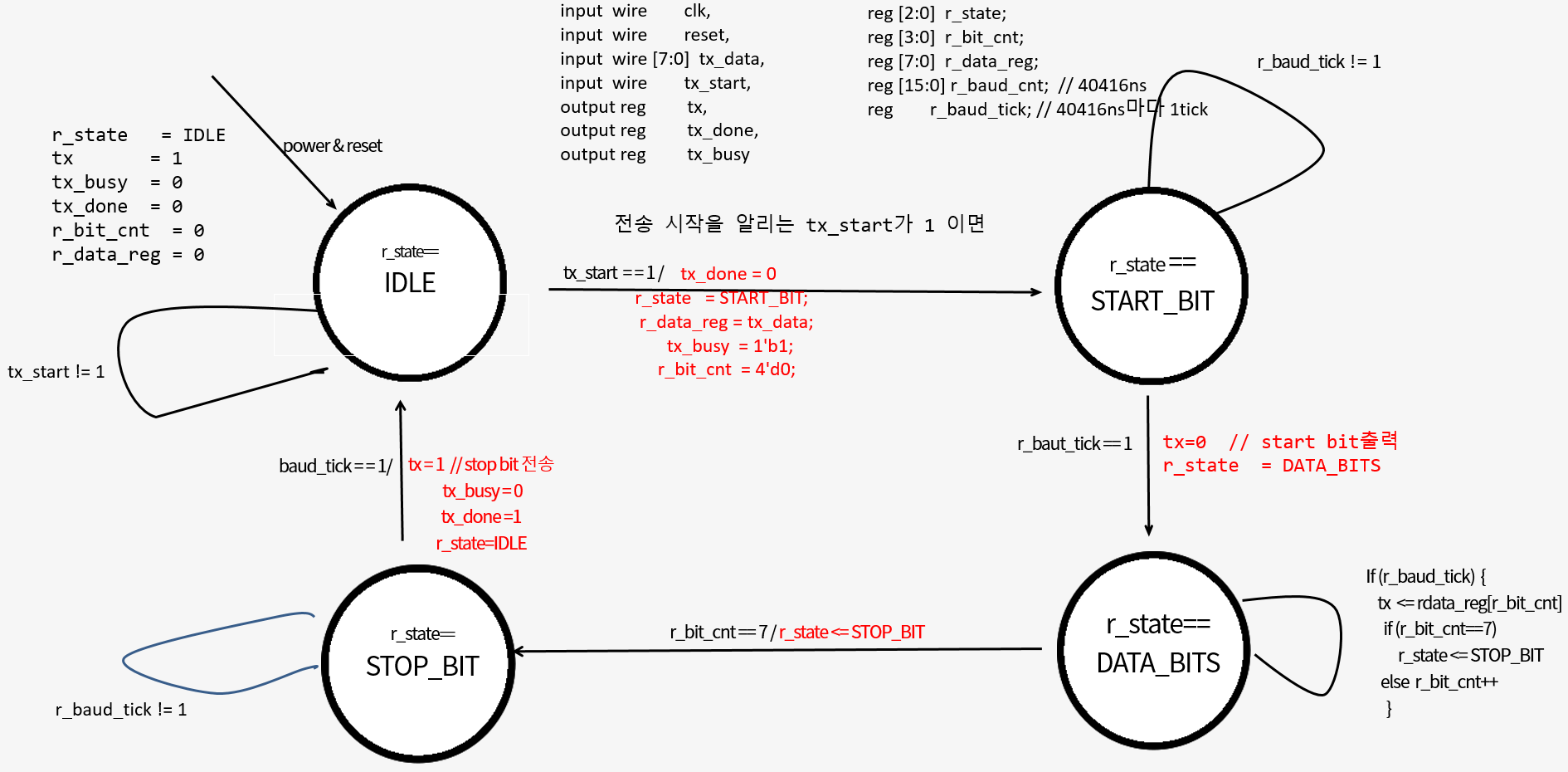

UART Transmit

1. 비동기 통신 방식으로, 송신(TX)과 수신(RX)이 독립적으로 처리됨.

송신과 수신은 각각 다른 타이밍에 발생할 수 있으며, 별도의 클럭 신호 없이 데이터를 송 · 수신함

2. 비동기이기 때문에 데이터를 받을 때, Start bit를 0으로 고정 후 데이터를 송 · 수신하고 마지막 끝 비트를 1로 고정시키는 인코딩 작업이 필요

3. 또한 송 · 수신시 Baud Rate를 고려해야 하기 때문에, 타이밍에 맞춰 인코딩 해야함

Step1 : START 신호로 low signal을 10416 ns 동안 전송(9600 BPS 기준)

Step2 : 이어서 8bit의 DATA를 LSB부터 MSB까지 0 이면 low, 1이면 high 로 10416 ns 주기로 전송

Step3 : DATA 전송을 마치고 high 로 유지

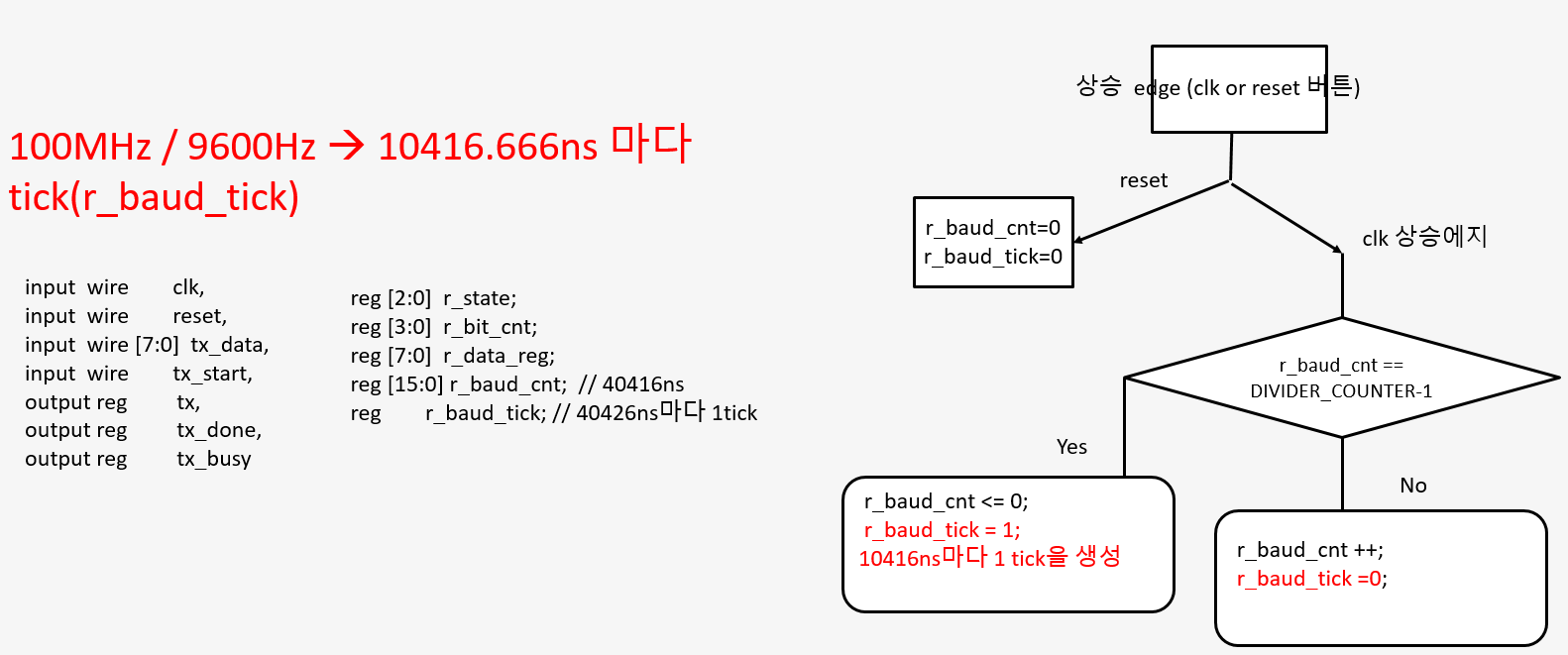

1. System clock 100MHz에서 9600Hz의 주파수를 만들고자 하면

1.1. 100MHz(100,000,000Hz) 의 1주기(1/100,000,000)는 0.000,000,01 sec(10ns)

1.2. System clock 100MHz를 입력으로 해서 9600Hz의 주파수를 만들고자 하면

1) 1주기는 100MHz / 9600Hz 10416.666ns(104.16us)

2) 결국 1주기가 10416.666ns 짜리 가 9600번 반복하면 100MHz(100,000,000Hz)가 생성 된다.

- system clock의 100MHz의 1주기가 10ns로써 10416.666ns를 count하기 위해서는 10416번 count 한다.

3) 여기서 50% Duty cycle을 유지 하고자 한다면 10416.666ns의 절반인 5208.333 ns

2. System clock이 100MHz에서 115200(bps)Hz의 주파수를 만들고자 하면

- 100,000,000Hz/115200bps = 868 (CLOCK PER BIT)

100MHz system clock의 115200bps 전송을 하기 위해서는 868clock당 1 bit를 송.수신 하면 됨

UART top module block diagram

UART controller module block diagram

UART 송신 module uart_tx

'(Telechips) AI 시스템 반도체 SW 개발자 교육 > Verilog HDL' 카테고리의 다른 글

| 18일차 (0) | 2025.07.28 |

|---|---|

| 13일차 (0) | 2025.07.16 |

| 10일차 (0) | 2025.07.14 |

| 9일차 (0) | 2025.07.10 |

| 8일차 (0) | 2025.07.09 |